我是 雪天鱼,一名FPGA爱好者,研究方向是FPGA架构探索。

关注公众号,拉你进“IC设计交流群”。

@

一、LEF简介

LEF是 Library Exchange Format 的缩写,描述了设计的库信息,库数据包括了 layer、via、placement site type 、macro cell 定义。

1.1 通用规则

- 标识符如 net name 、cell name 都限制在2048字符以内

- 距离定义单位为微米。

- 距离精度由

UNITS语句控制 - LEF语句以分号(

;)结尾. 语句的最后一个字符与分号之间必须有一个空格。

1.2 管理 LEF 文件

可以在一个 LEF 文件中定义设计所需的所有的库信息;但这样做将创建一个复杂且难以管理的大文件。所以可以将库信息分成两个文件,一个是“technology”LEF文件,另一个是“cell library”LEF文件。

- technology LEF file:工艺 LEF 文件包含设计的所有工艺信息,例如布局布线设计规则以及层的处理信息。一个 technology LEF 文件可以包括以下任何一个LEF语句:

[VERSION statement]

[BUSBITCHARS statement]

[DIVIDERCHAR statement]

[UNITS statement]

[MANUFACTURINGGRID statement]

[USEMINSPACING statement]

[CLEARANCEMEASURE statement ;]

[PROPERTYDEFINITIONS statement]

[FIXEDMASK ;]

[LAYER (Nonrouting) statement

| LAYER (Routing) statement] ...

[MAXVIASTACK statement]

[VIA statement] ...

[VIARULE statement] ...

[VIARULE GENERATE statement] ...

[NONDEFAULTRULE statement] ...

[SITE statement] ...

[BEGINEXT statement] ...

[END LIBRARY]

- cell library LEF file :单元库LEF文件包含设计所需的宏和标准单元信息。

库LEF文件可以包含以下任何LEF语句:

[VERSION statement]

[BUSBITCHARS statement]

[DIVIDERCHAR statement]

[VIA statement] ...

[SITE statement]

[MACRO statement

[PIN statement] ...

[OBS statement ...] ] ...

[BEGINEXT statement] ...

[END LIBRARY]

注:读取 LEF 文件时,必须先读取 technology LEF file,因为在 cell library LEF file 中会用到在

technology LEF file 定义的一些库信息。

二、Layer (Cut)

通过分配名称和设计规则来定义每个 cut 层。每个 cut 层都必须分开定义。由低而上的顺序中定义图层。例如:

poly masterslice

cut01 cut

metal1 routing

cut12 cut

metal2 routing

cut23 cut

metal3 routing

这个对做过版图的朋友而言应该很容易理解,就是 poly + via + metal1 + via1 + metal2 + via2 +...多层叠加,cut 层实际上就是用来定义 vias的。

语法:

LAYER layerName

TYPE CUT ;

[MASK maskNum ;]

[SPACING cutSpacing

[CENTERTOCENTER]

[SAMENET]

[ LAYER secondLayerName [STACK]

| ADJACENTCUTS {2 | 3 | 4} WITHIN cutWithin [EXCEPTSAMEPGNET]

| PARALLELOVERLAP

| AREA cutArea

]

;] ...

[SPACINGTABLE ORTHOGONAL

{WITHIN cutWithin SPACING orthoSpacing} ... ;]

[ARRAYSPACING [LONGARRAY] [WIDTH viaWidth] CUTSPACING cutSpacing

{ARRAYCUTS arrayCuts SPACING arraySpacing} ... ;]

[WIDTH minWidth ;]

[ENCLOSURE [ABOVE | BELOW] overhang1 overhang2

[ WIDTH minWidth [EXCEPTEXTRACUT cutWithin]

| LENGTH minLength]

;] ...

[PREFERENCLOSURE [ABOVE | BELOW] overhang1 overhang2 [WIDTH minWidth] ;] ...

[RESISTANCE resistancePerCut ;]

[PROPERTY propName propVal ;] ...

[ACCURRENTDENSITY {PEAK | AVERAGE | RMS}

{ value

| FREQUENCY freq_1 freq_2 ... ;

[CUTAREA cutArea_1 cutArea_2 ... ;]

TABLEENTRIES

v_freq_1_cutArea_1 v_freq_1_cutArea_2 ...

v_freq_2_cutArea_1 v_freq_2_cutArea_2 ...

...

} ;]

[DCCURRENTDENSITY AVERAGE

{ value

| CUTAREA cutArea_1 cutArea_2 ... ;

TABLEENTRIES value_1 value_2 ...

} ;]

[ANTENNAMODEL {OXIDE1 | OXIDE2 | OXIDE3 | OXIDE4} ;] ...

[ANTENNAAREARATIO value ;] ...

[ANTENNADIFFAREARATIO {value | PWL ( ( d1 r1 ) ( d2 r2 ) ...)} ;] ...

[ANTENNACUMAREARATIO value ;] ...

[ANTENNACUMDIFFAREARATIO {value | PWL ( ( d1 r1 ) ( d2 r2 ) ...)} ;] ...

[ANTENNAAREAFACTOR value [DIFFUSEONLY] ;] ...

[ANTENNACUMROUTINGPLUSCUT ;]

[ANTENNAGATEPLUSDIFF plusDiffFactor ;]

[ANTENNAAREAMINUSDIFF minusDiffFactor ;]

[ANTENNAAREADIFFREDUCEPWL

( ( diffArea1 diffAreaFactor1 ) ( diffArea2 diffAreaFactor2 ) ...) ; ]

END layerName

实例:

LAYER mcon

TYPE CUT ;

WIDTH 0.17 ; # Mcon 1

SPACING 0.19 ; # Mcon 2

ENCLOSURE BELOW 0 0 ; # Mcon 4

ENCLOSURE ABOVE 0.03 0.06 ; # Met1 4 / Met1 5

ANTENNADIFFAREARATIO PWL ( ( 0 3 ) ( 0.0125 3 ) ( 0.0225 3.405 ) ( 22.5 408 ) ) ;

DCCURRENTDENSITY AVERAGE 0.36 ; # mA per via Iavg_max at Tj = 90oC

END mcon

这里由于涉及的语法很多,就不一一讲解了,等后面用到时,再进行更新,先对上面的实例进行讲解。

| 语句 | 描述 |

|---|---|

| WIDTH | 通孔宽度(正方形) |

| SPACING | 通孔之间最小间距 |

| ENCLOSURE | BELOW :指定通孔边界与下方相邻金属层边界的最小间距 ABOVE:指定通孔边界与上方相邻金属层边界的最小间距 |

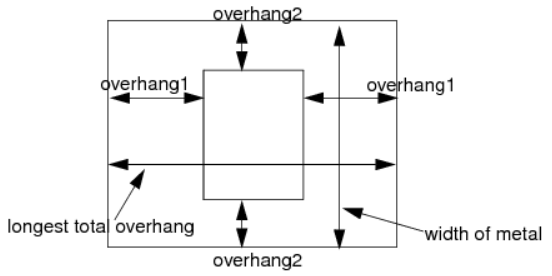

看图解释,通孔宽度也就是指的上图中间方块(这里有点像长方形了)的宽度,overhang1 是指的通孔左右两边距离金属边界的间距,overhang2 是指的通孔上下两边距离金属边界的间距。

而 SPACING 就是指的通孔之间的间距。

三、Layer(Masterslice or Overlap)

在设计中定义 MasterSlice(非布线)或 overlap layers。 Masterslice layers 通常是多晶硅层,只有在宏单元在多晶硅层上有 pins 时才会定义。

语法:

LAYER layerName

TYPE {MASTERSLICE | OVERLAP} ;

[MASK maskNum ;]

[PROPERTY propName propVal ;] ...

[PROPERTY LEF58_TYPE

"TYPE [NWELL | PWELL | ABOVEDIEEDGE | BELOWDIEEDGE | DIFFUSION | TRIMPOLY | TRIMMETAL | REGION]

];" ;

[PROPERTY LEF58_TRIMMEDMETAL

"TRIMMEDMETAL metalLayer [MASK maskNum]

]; " ;

END layerName

| 语句 | 描述 |

|---|---|

| LAYER layerName | 指定该层的名称。此名称将在以后引用该层时使用。 |

| TYPE | 指定层的用途 ,有两种 - MASTERSLICE : 层固定在基座阵列中。如果 pins 出现在 MASTERSLICE 层中,则必须定义 vias 以允许布线器连接那些 pin 和第一个布线层。Masterslice层不允许用来布线。在 MASTERSLICE 层和相邻布线层之间必须定义一个 cut 层 - OVERLAP: 用于直线块重叠检查的图层。 |

实例:

LAYER nwell

TYPE MASTERSLICE ;

PROPERTY LEF58_TYPE "TYPE NWELL ;" ;

END nwell

LAYER pwell

TYPE MASTERSLICE ;

PROPERTY LEF58_TYPE "TYPE PWELL ;" ;

END pwell

- 更多技术文章和学习资料,请关注我的公众号:【集成电路设计教程】

- 全平台统一:【雪天鱼】

文章来源: 博客园

- 还没有人评论,欢迎说说您的想法!

客服

客服