ZYNQ:赛灵思公司(Xilinx)推出的行业第一个可扩展处理平台Zynq系列。旨在为视频监视、汽车驾驶员辅助以及工厂自动化等高端嵌入式应用提供所需的处理与计算性能水平。

Zynq-7000可扩展处理平台是采用赛灵思新一代FPGA(Artix-7与Kintex-7FPGA)所采用的同一28nm可编程技术的最新产品系列。可编程逻辑可由用户配置,并通过“互连”模块连接在一起,这样可以提供用户自定义的任意逻辑功能,从而扩展处理系统的性能及功能。不过,与采用嵌入式处理器的FPGA不同,Zynq-7000产品系列的处理系统不仅能在开机时启动,而且还可根据需要配置可编程逻辑。采用这种方法,软件编程模式与全功能的标准ARM处理SoC毫无二致。

现在用Vivado软件对ZYNQ-7000开发板进行第一个程序设计:Hello World。

一、新建Vivado工程

1.打开Vivado,新建一个工程,Next

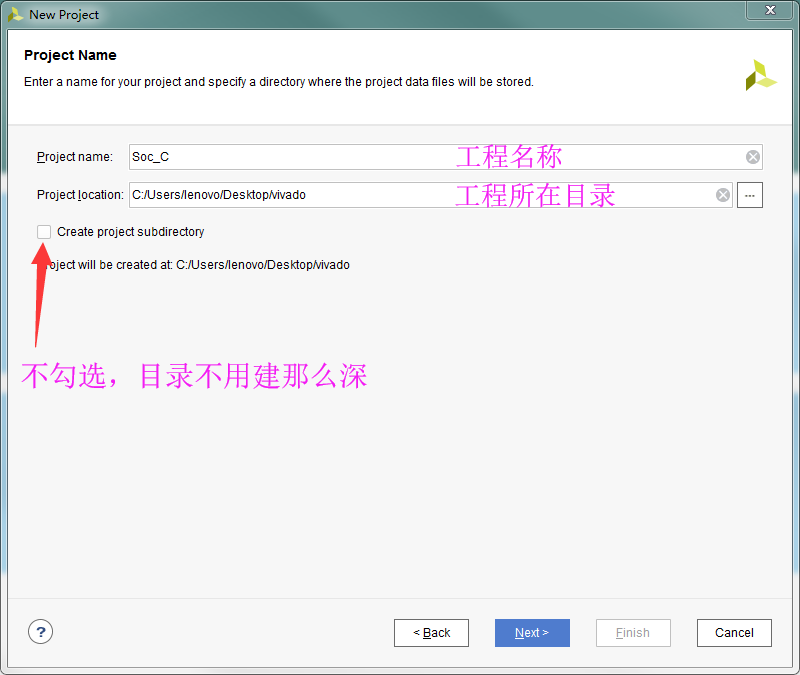

2.设置工程名称和工程所在目录,Next

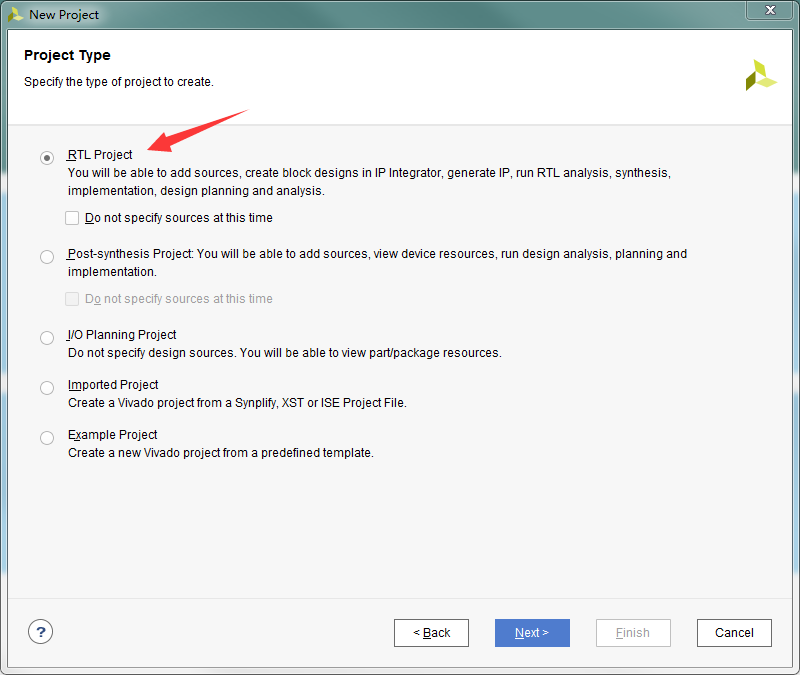

3.选择第一项:RTL Project,Next

4.添加资源,可以直接Next

5.添加约束,可以直接Next

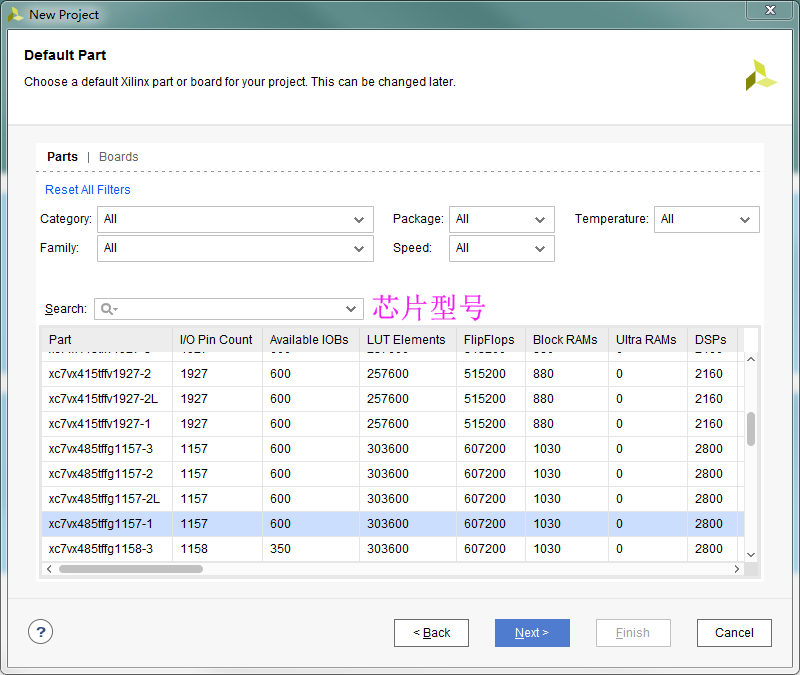

6.芯片型号选择xc7z020clg400-1,Next

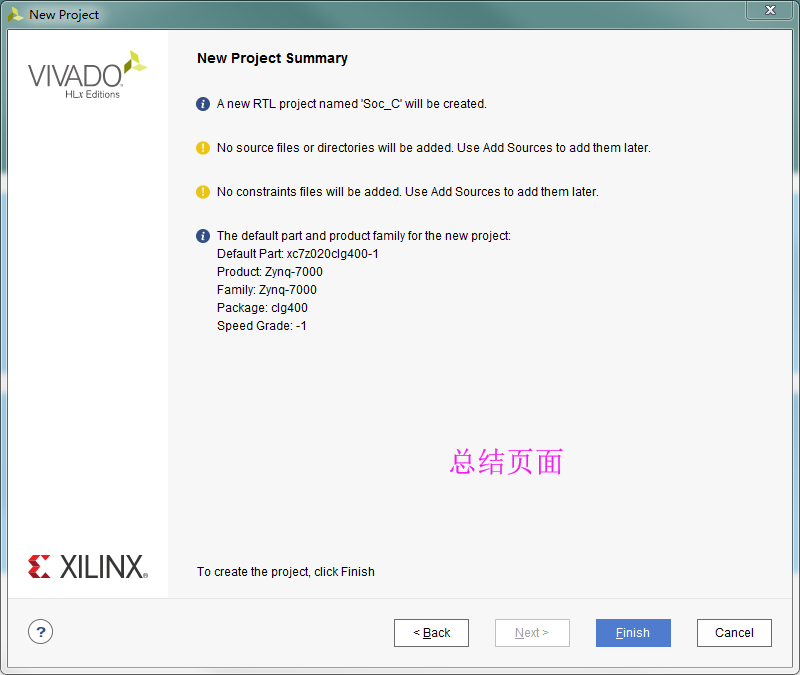

7.总结页面,Finish

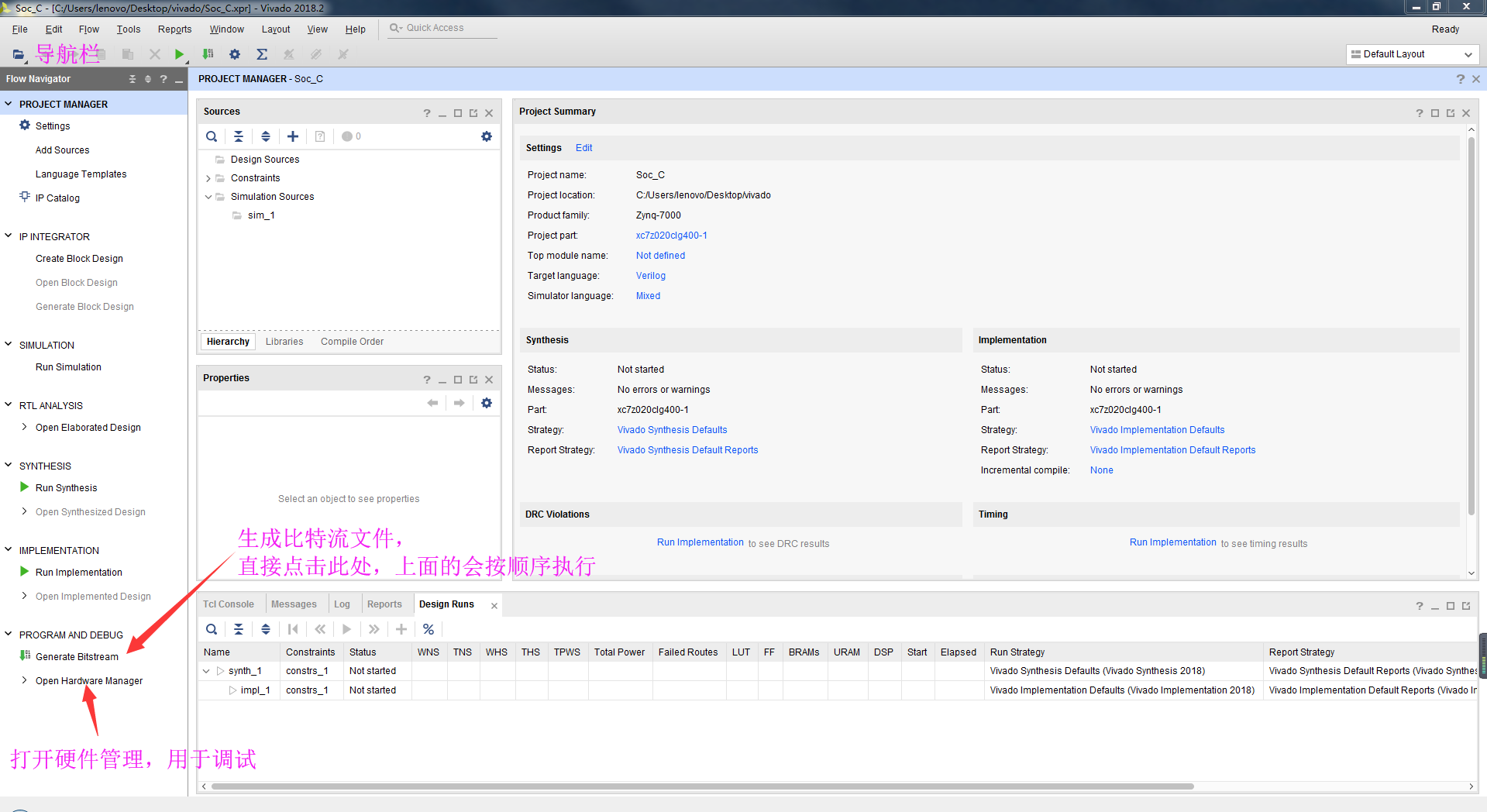

8.进入Vivado工程页面,左边是导航栏,可以直接点击Generate Bitstream,上面的选项也会按顺序被执行。Open Hardware Manager则是硬件管理,用于下载、调试等。

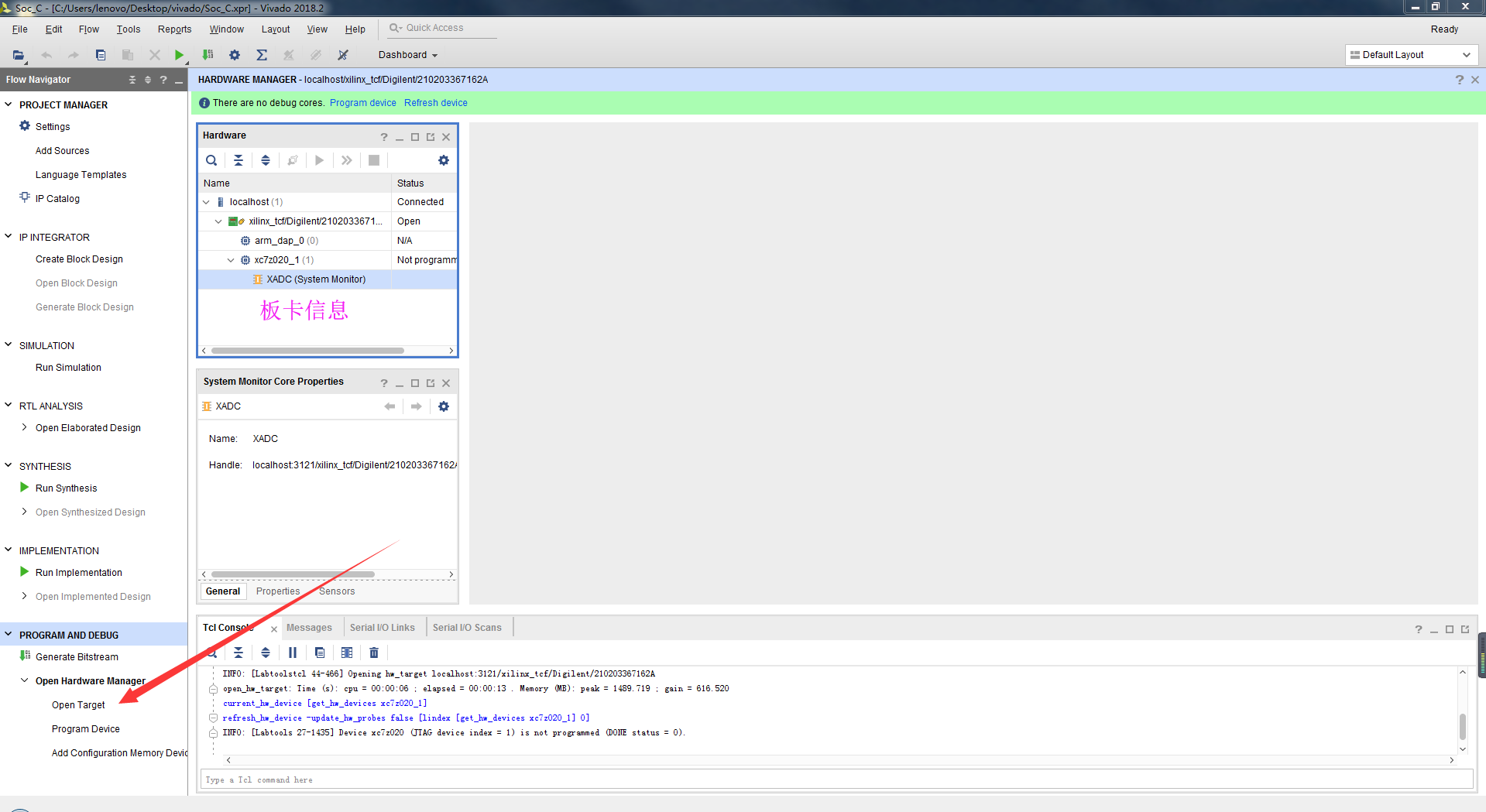

9.如果连接好了板卡,那么点击Open Hardware Manager --- Open Target则可以看到板卡信息。

二、ZYNQ IP核设置

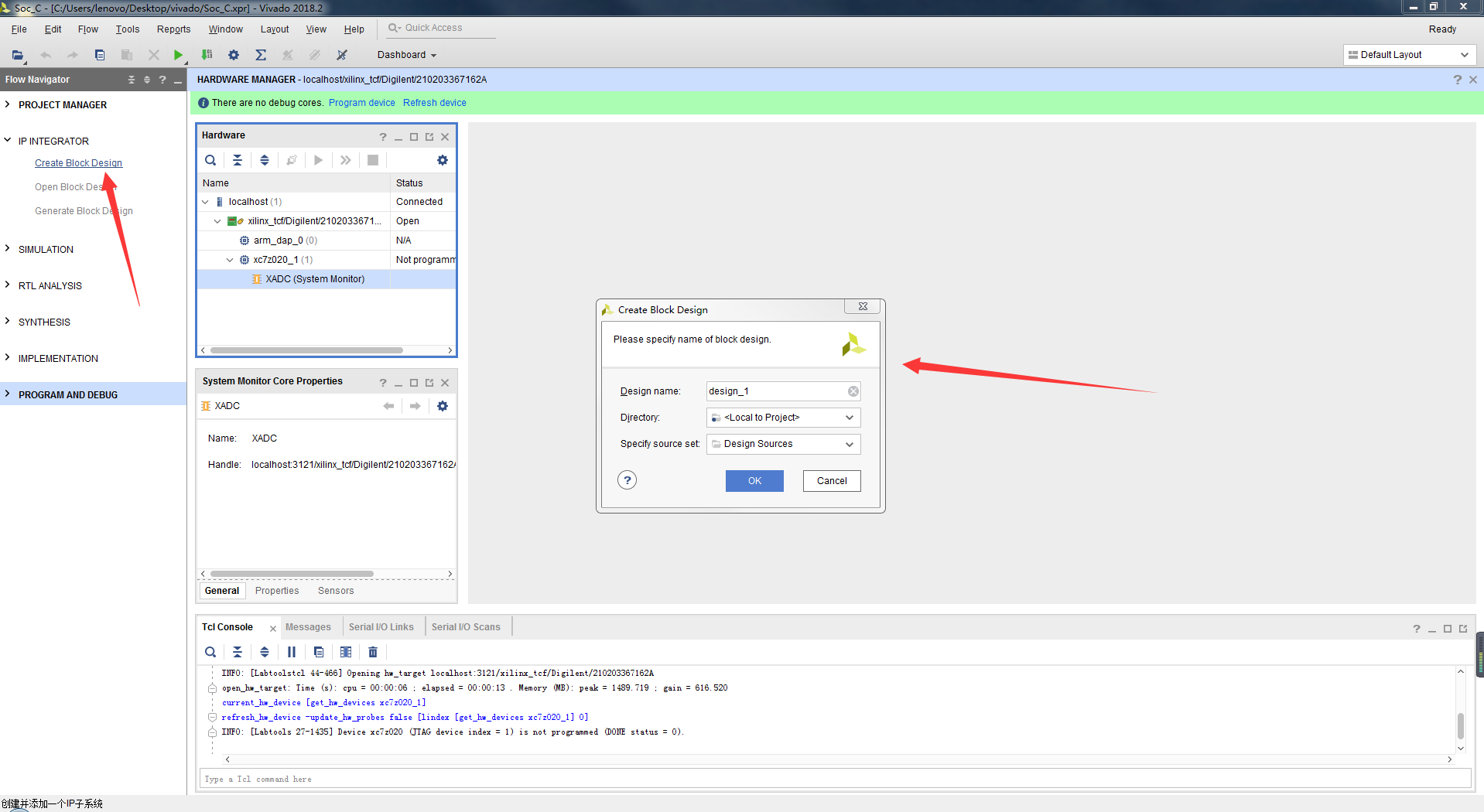

1.点击导航栏的 IP INTEGRATOR --- Create Block Design,弹出工程名称和工程位置,填写后点OK

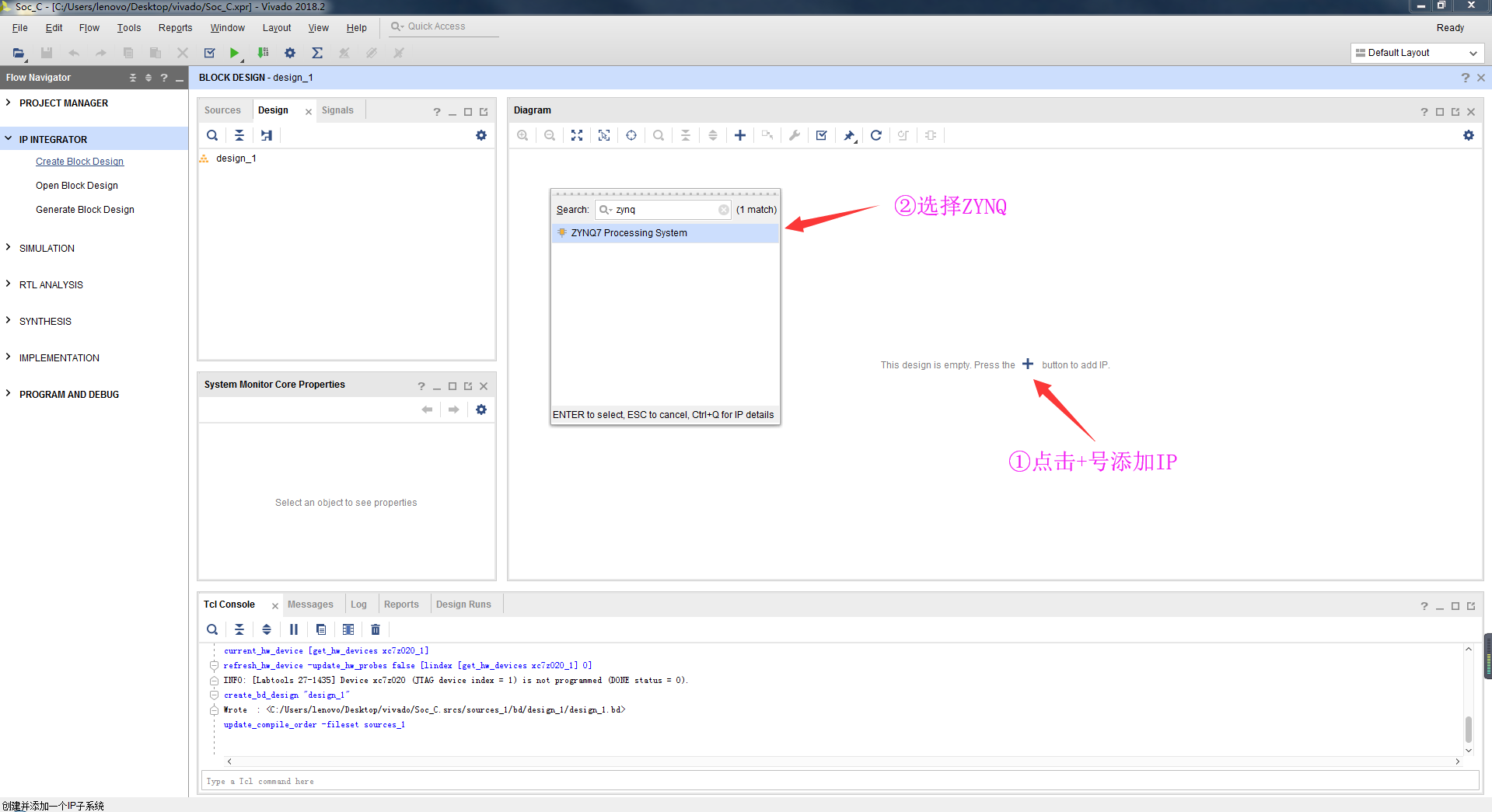

2.点击中间的 + 号添加IP,然后在弹出的小窗口中选择ZYNQ,双击该IP核

3.此时看到ZYNQ的接口界面,有几个引脚,我们只需要最简单的系统,双击ZYNQ进行参数设置

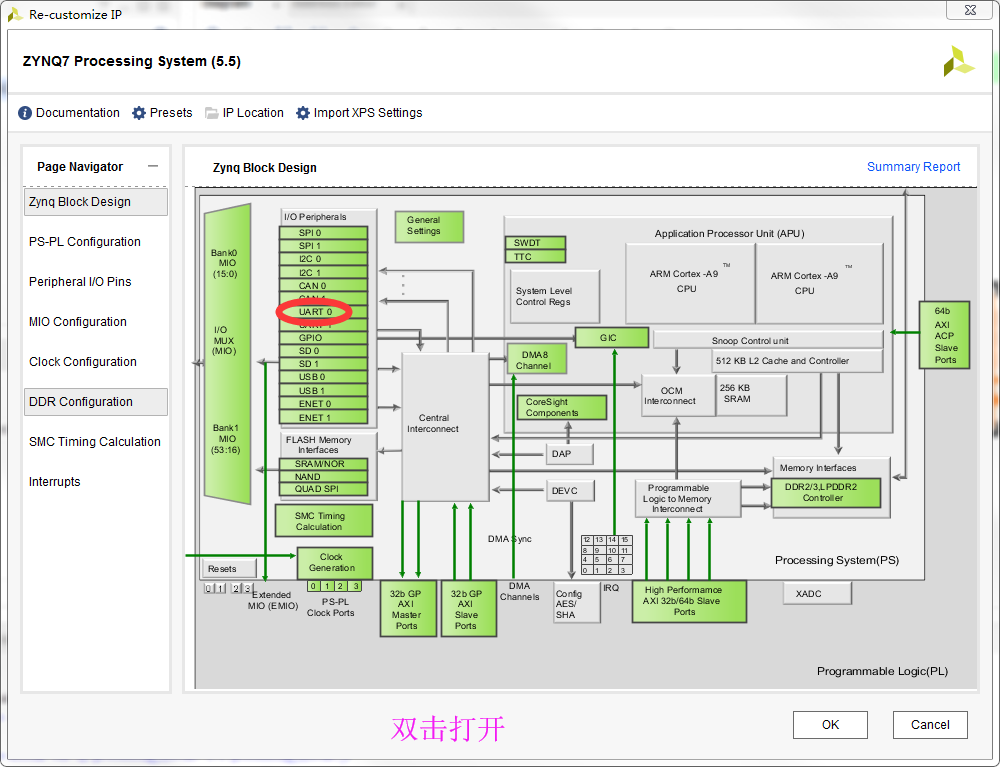

4.进入到ZYNQ内部资源区域,本实验仅需要用到串口,因此双击UART 0

5.打开新的窗口,选择MIO Configuration,电压设置成LVCMOS 1.8V,用到了SD和UART,因此勾选它们并且设置引脚编号。

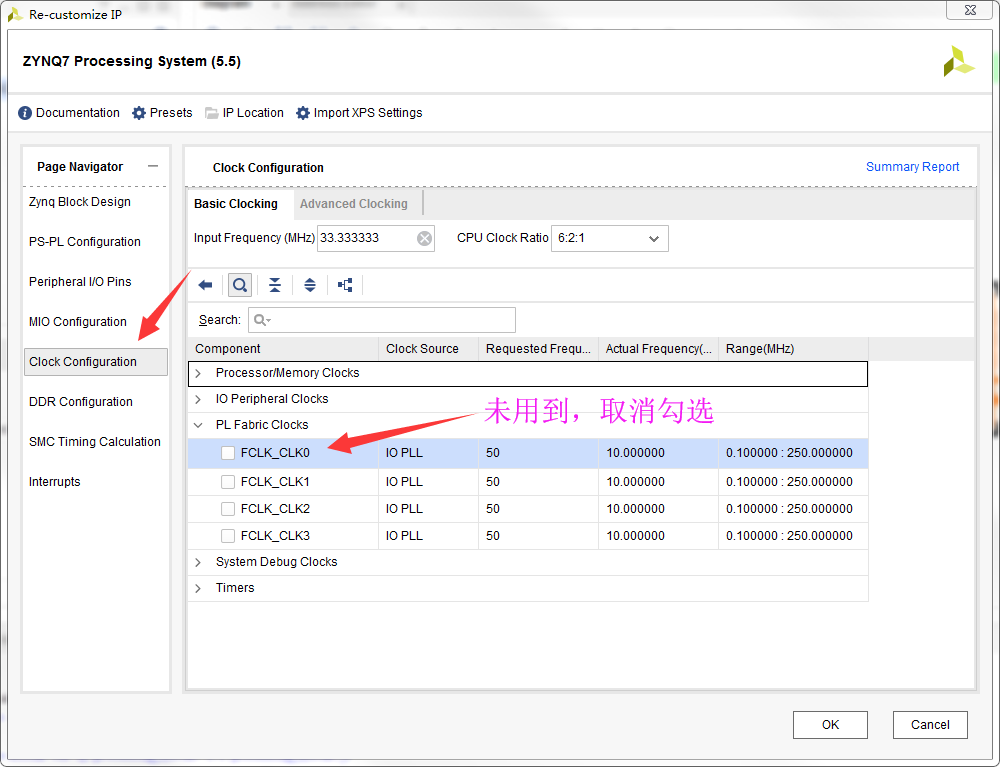

6.选择Clock Configuration,本实验没有用到FPGA板卡时钟,因此取消勾选

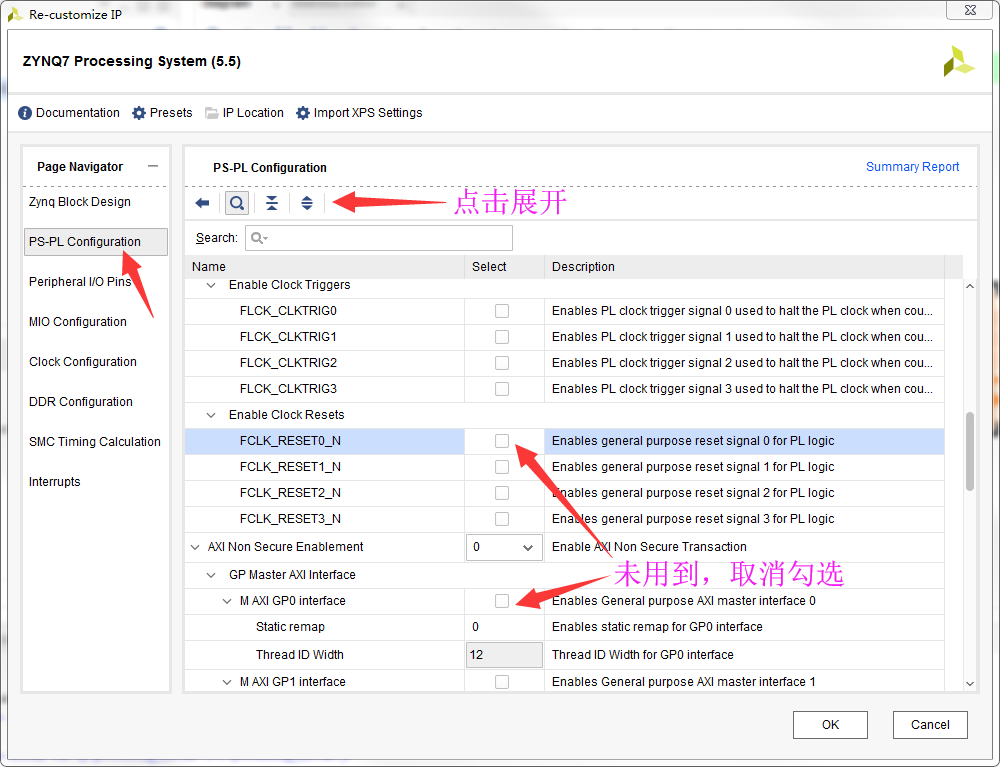

7.选择PS-PL Configuration,取消勾选以下选项

8.选择DDR Configuration,勾选Enable DDR,点击展开,对DDR进行一些参数设置,之后点击OK

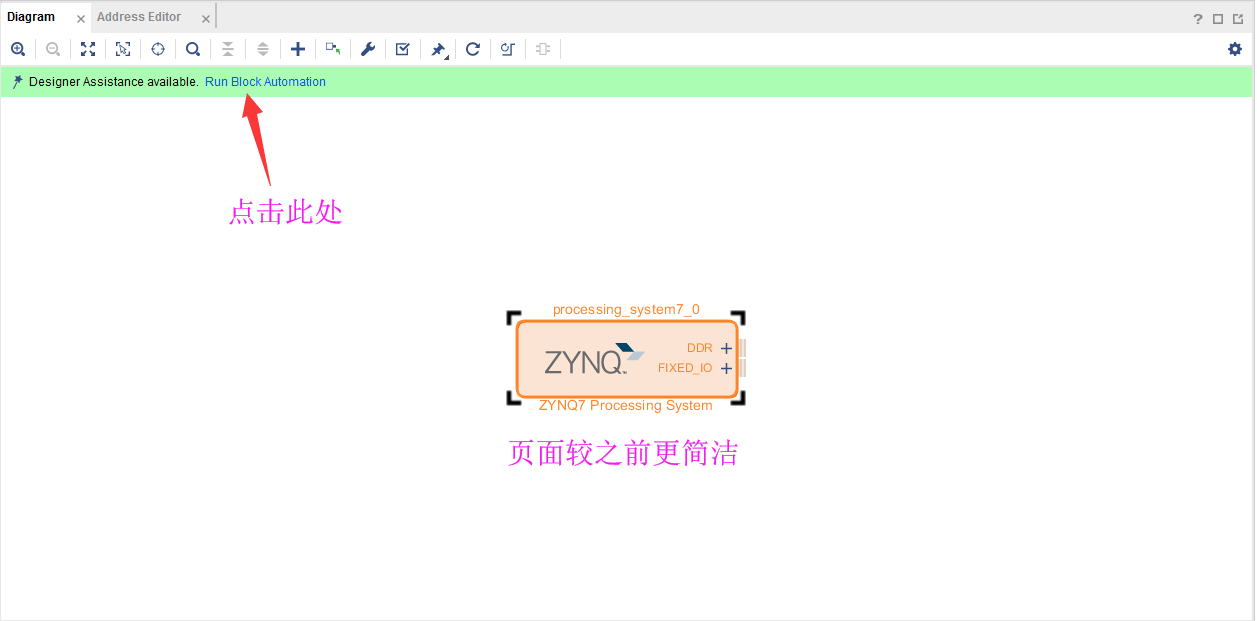

9.回归到ZYNQ主页面,可以看到比之前更简洁了。上面绿色横条处点击Run Block Automation

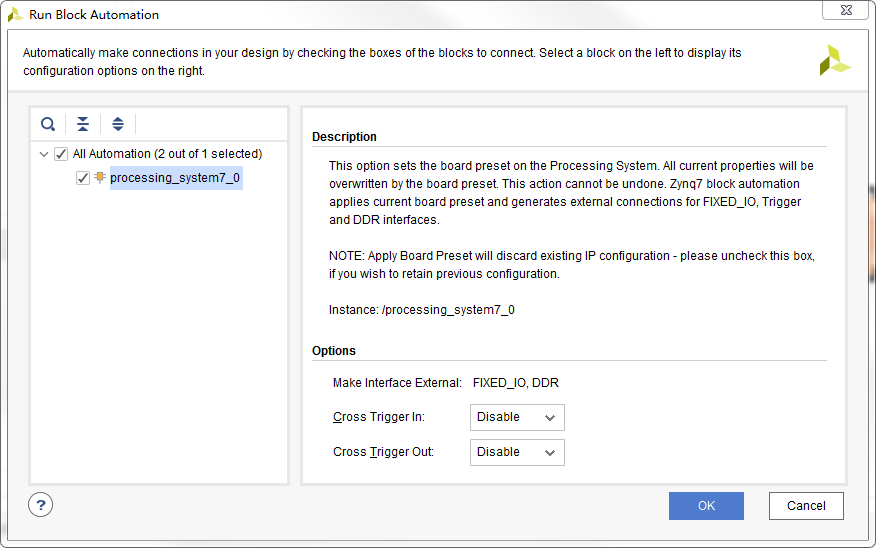

10.点击OK

11.ZYNQ变成了如下的结构图。

12.可以设置让Vivado管理我们的文件,点击Sources,选择黄色的工程,右键选择Create HDL Wrapper,弹出一个小页面,点击OK

三、使用SDK进行软件开发

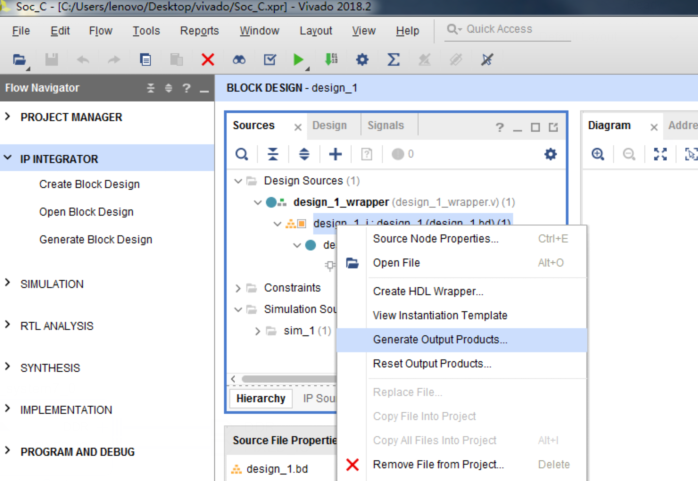

1.右键点击Generate Output Products,可以生成Bit流文件。全局模式能综合生成全面网表,速度更慢,OOC模式在代码不规范时会有问题,但速度更快,我们选择OOC模式。

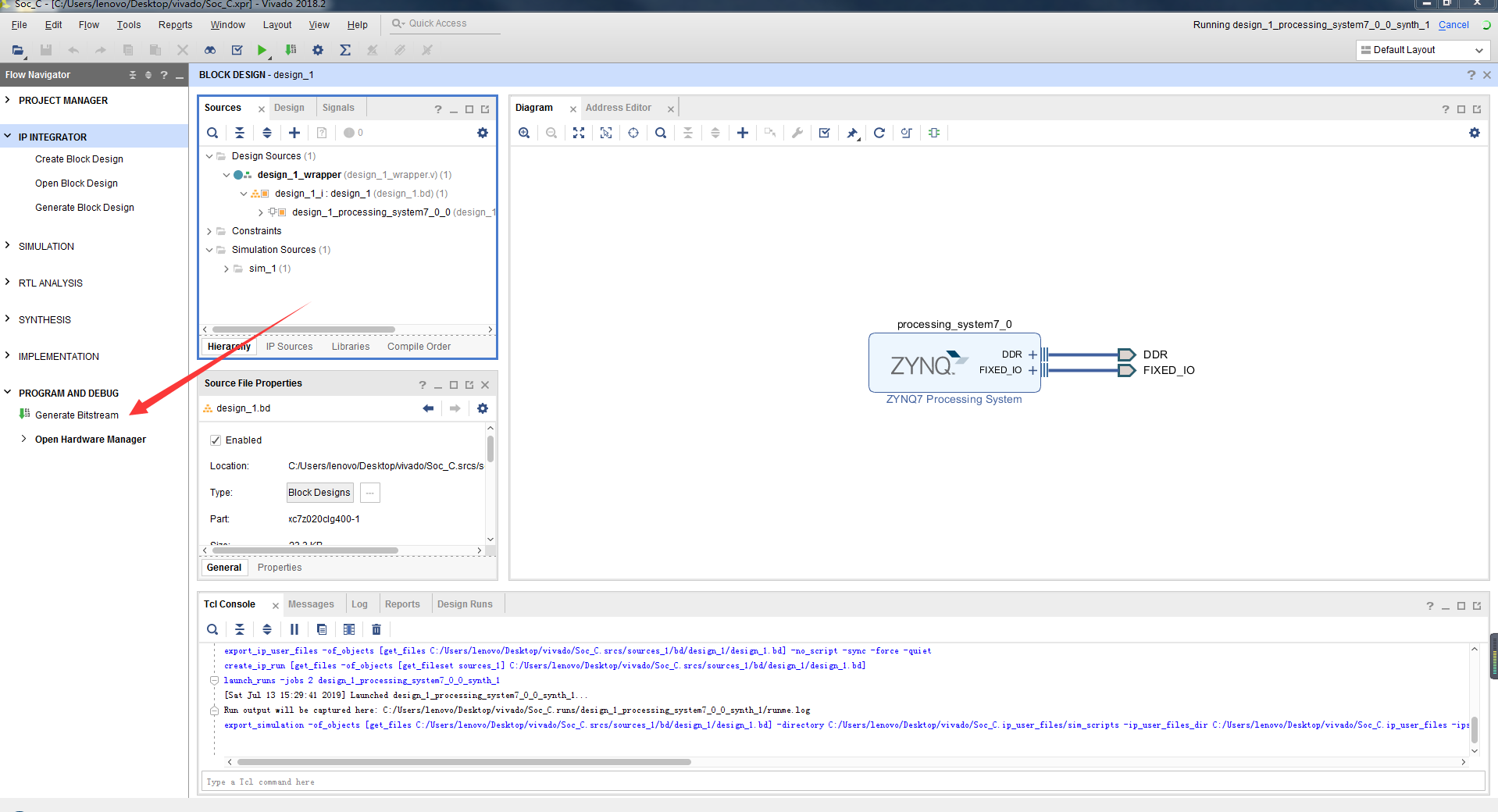

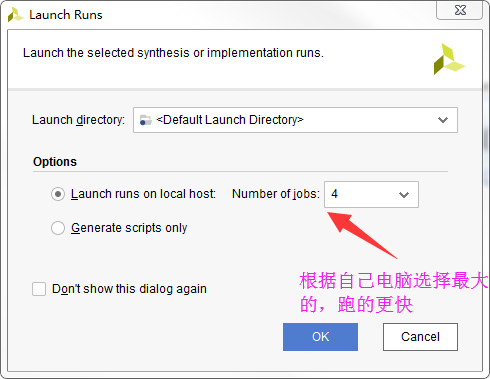

2.当然,你也可以直接点击导航栏中的Generate Bitsteam,会弹出一个选择框,可以根据自己电脑性能选择最大的,这样跑的更快。

3.如果弹出如下界面,选择OK则会显示内部结构,电脑容易卡住,我们不需要用到这个,所以选择Cancel

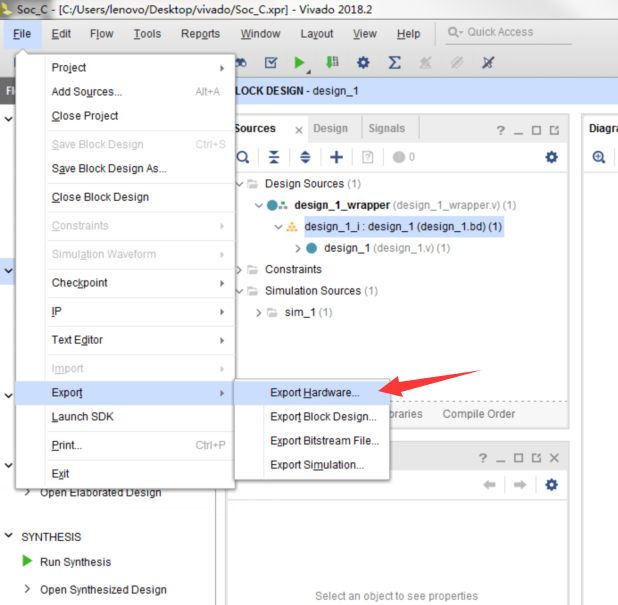

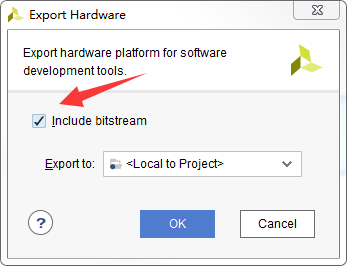

4.将生成的硬件描述文件导出到SDK开发目录,点击File --- Export --- Export Hardware,勾选Include bitstream后点OK

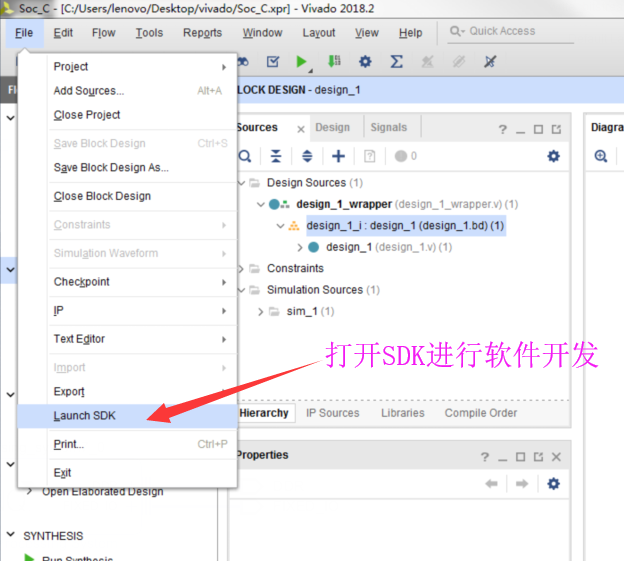

5.启动SDK,点击File Launch SDK,弹出的小窗口直接点OK就行

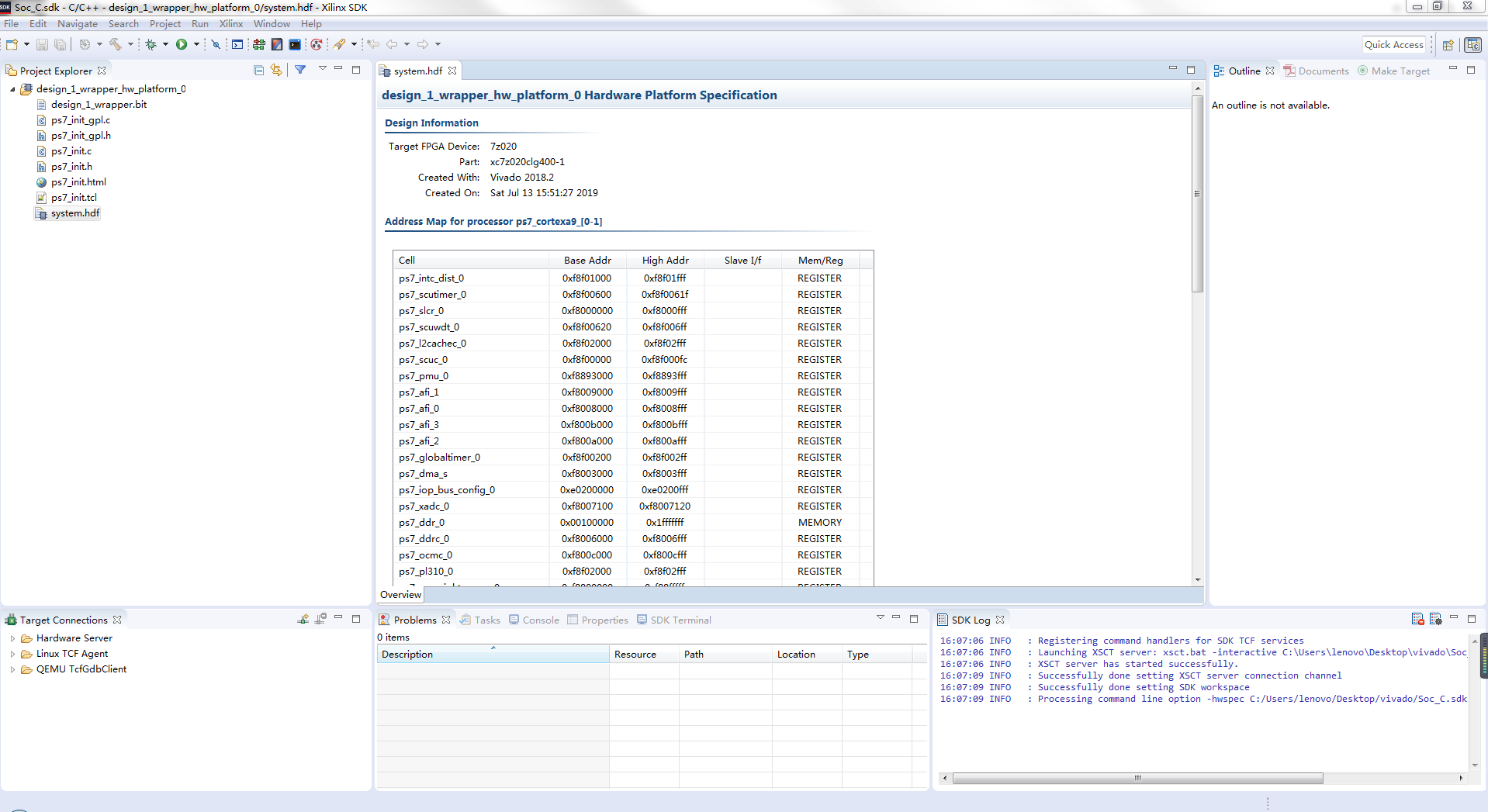

6.如图所示便是SDK软件开发界面了。

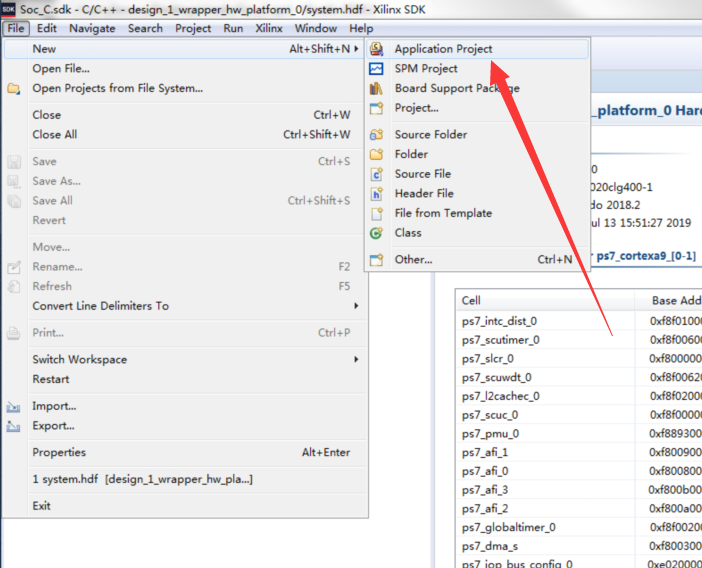

7.新建一个软件的APP,用于后面的C语言编程。点击File --- New --- Application Project

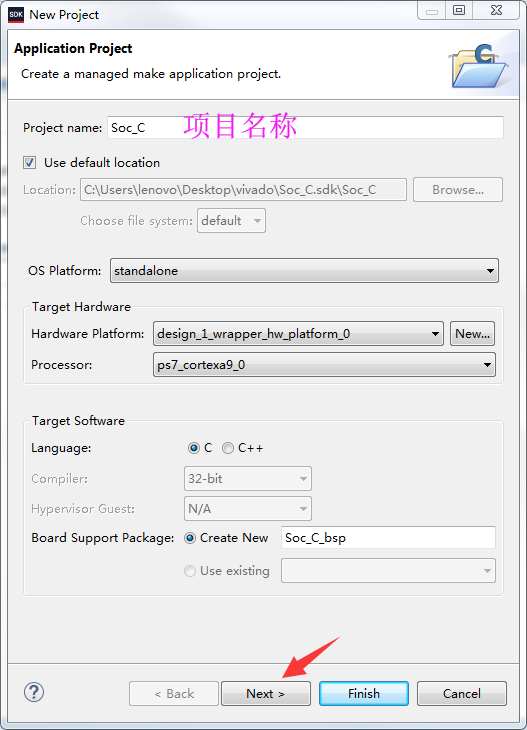

8.填写项目名称,点击Next

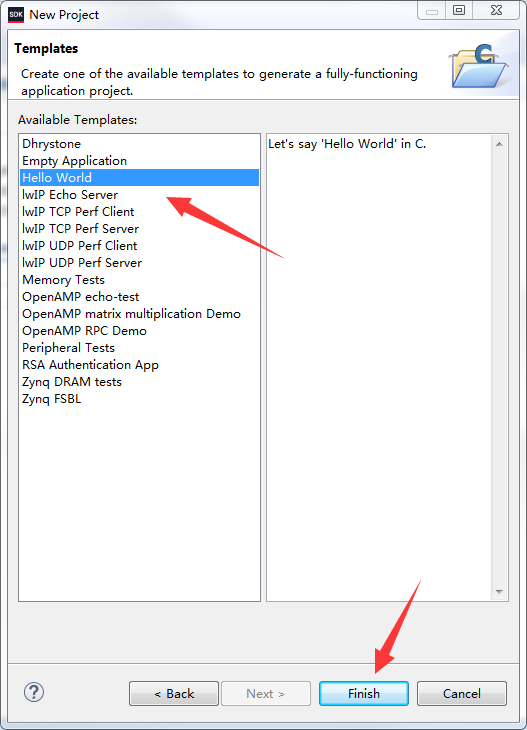

9.选择Hello World,点击Finish

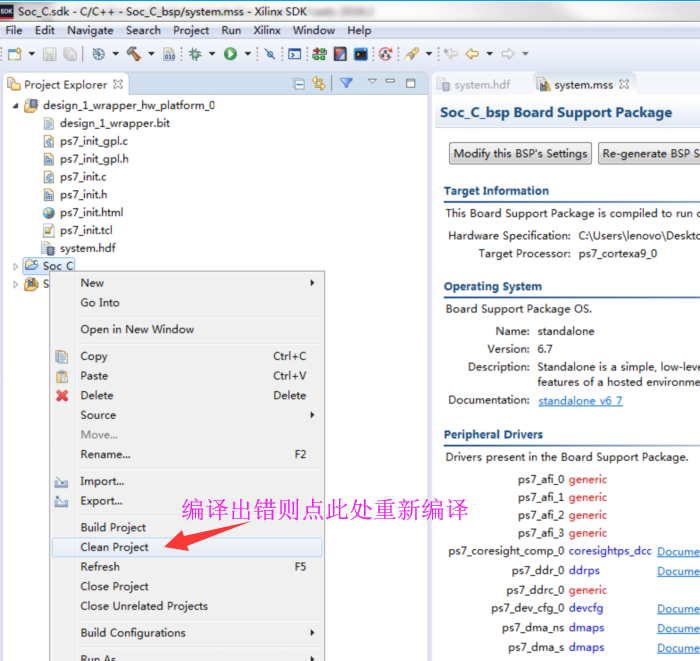

10.此时软件自动开始编译,编译完成后出现Hello World 的程序,如果编译出错,可以点击如下所示选项重新编译。

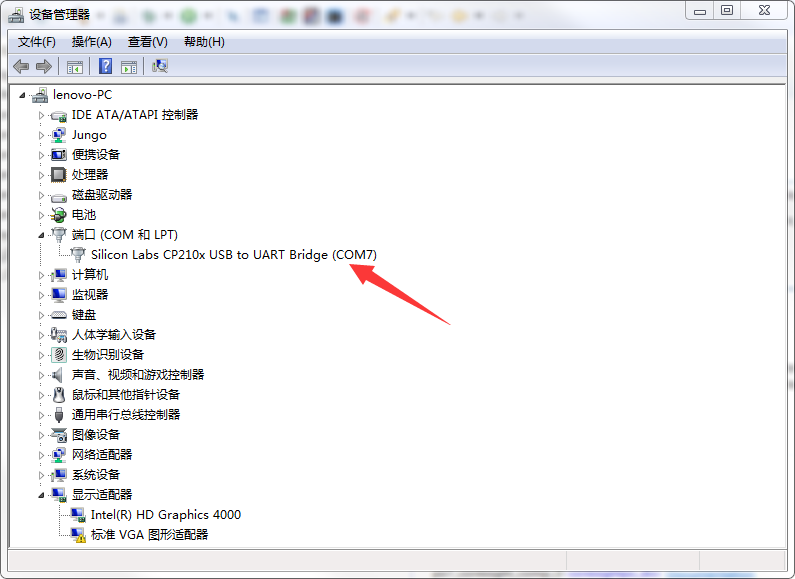

11.本实验需要用到Uart串口,我们打开我的电脑 --- 设备管理器 --- 端口,检查是否已经连接好串口

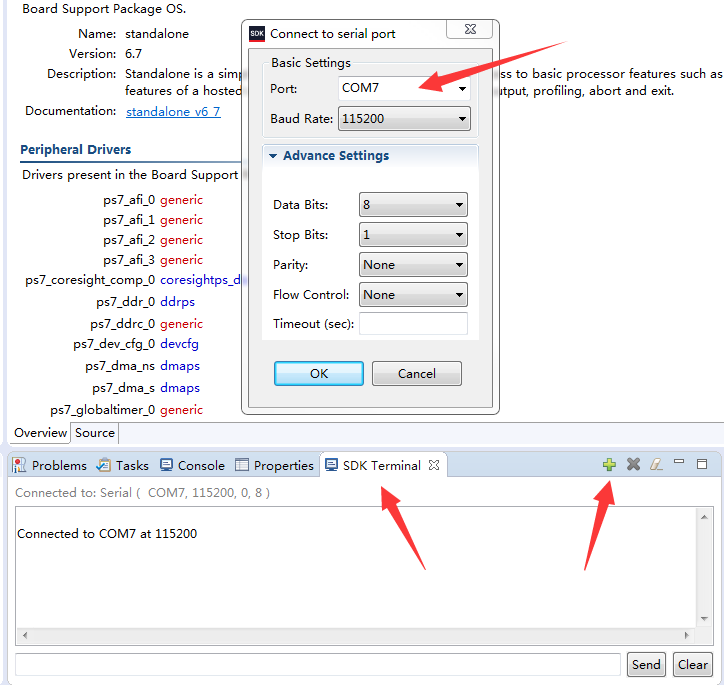

12.回到SDK界面,看到界面下方有一个SDK Terminal,点击该选项,并且点击那个+号,设置其自带的串口工具的参数。

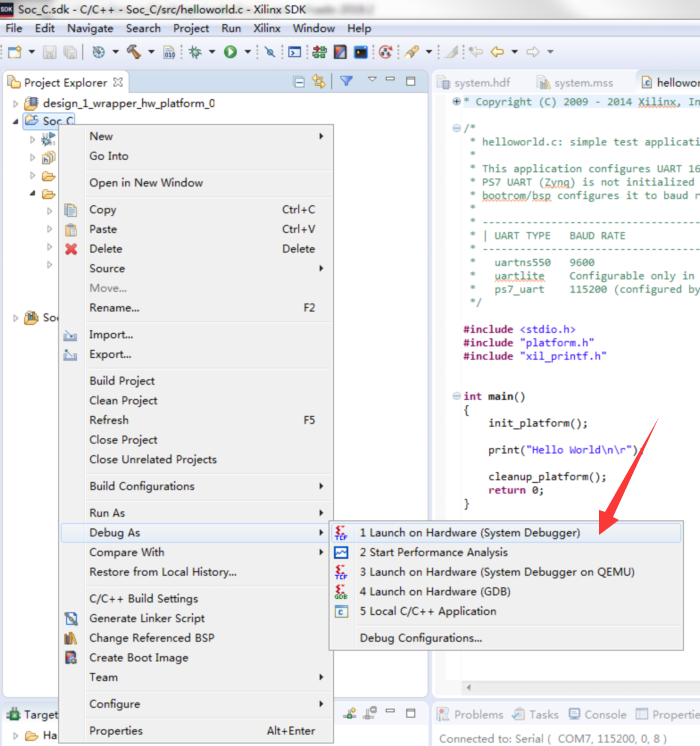

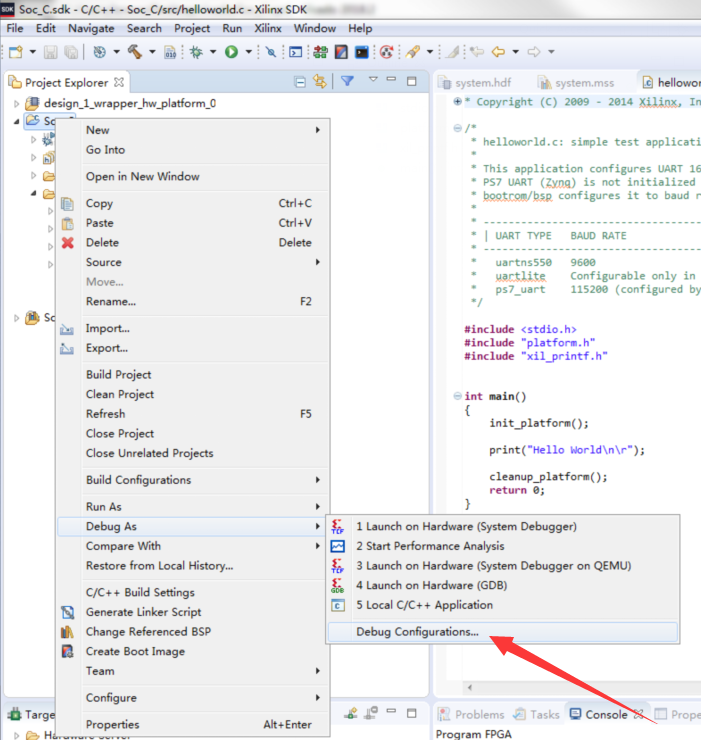

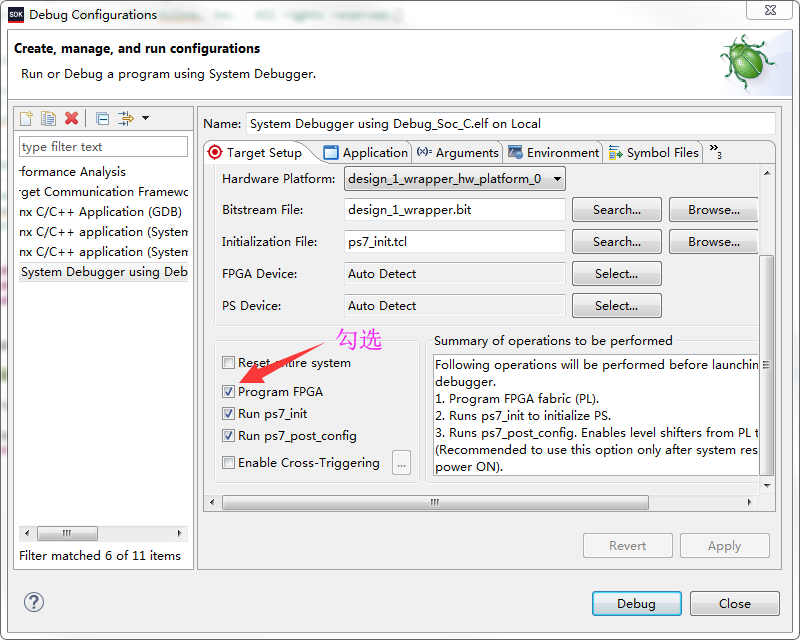

13.点击如下选项

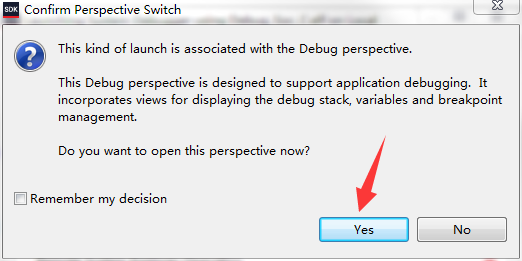

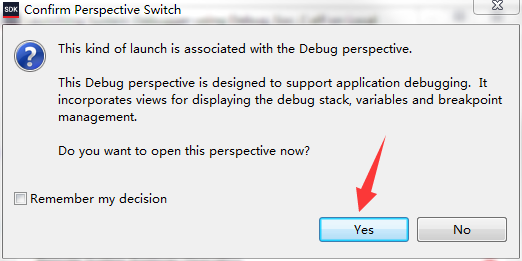

14.如果跳出如下界面,点击No

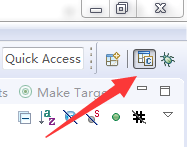

15.点击右上角的按钮可以进行界面切换

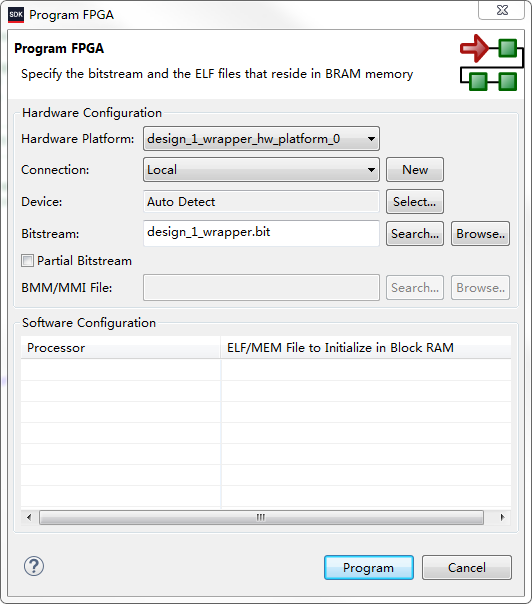

16.点击如下图标可以进行FPGA配置,点击Program将程序烧录进板卡,这时跳出小窗口就要选择yes了。

17.当然,你也可以点击这个选项进行FPGA配置,这时跳出小窗口就要选择yes了。

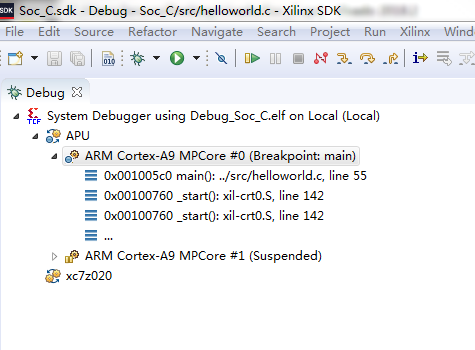

18.页面出现如下的文件目录,表示成功。

19.界面上方有几个调试选项:

Resume:运行到断点为止

Step into:进到函数内部

Step over:单步调试

Step return:跳出函数内部

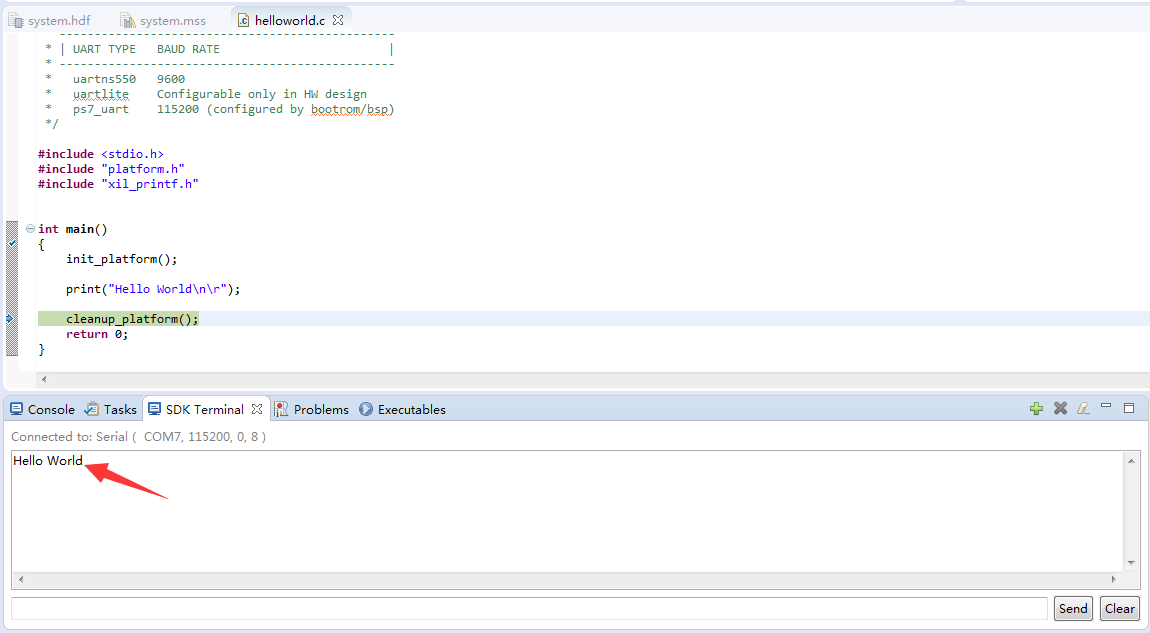

这里选择单步调试即可,可以看到界面下方的SDK Terminal中显示出:Hello World

20.当然,也可以使用电脑里的窗口助手软件进行接收,先在SDK Terminal界面中点击X关闭该功能,然后打开电脑里的串口助手,助手需要打开处于可以工作状态,接收设置成ASCII模式。重新回到SDK界面运行程序,可以看到串口助手同样显示出:Hello World

四、后记

用了ISE才知道Quartus多么的好用,用了Vivado才知道ISE多么的好用。Vivado界面还是蛮复杂的,不过万事开头难,我希望不久就能熟练运用起来,工具不应该成为限制我们进步的阻碍!

客服

客服

真好!赞赞赞