背景:

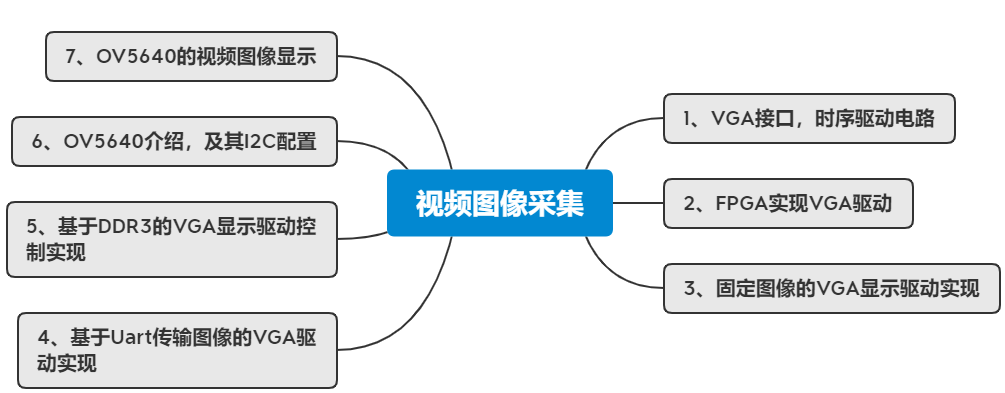

本系列是为了学习了图像处理,视频采集系统搭建。将自己学过的几个图像处理的基础算法,做过的设计记录下来,计划是这样的:

①:理论介绍,

②:先搭建一个VGA时序系统,显示方格图,竖条纹图之类的,算是基本入门

③:搭建一个固定图像的VGA显示,

④:搭建一个使用PC端上位机通过串口发送一幅图片数据到FPGA开发板,FPGA接收数据并做处理最终发送给VGA显示屏显示

⑤:基于DDR3的VGA显示驱动控制实现

⑥:OV5640介绍,及其IIC配置

⑦:OV5640的视频图像显示

上述均不涉及图像算法设计

视频图像采集之——VGA接口与时序电路(1)

关于VGA描述:

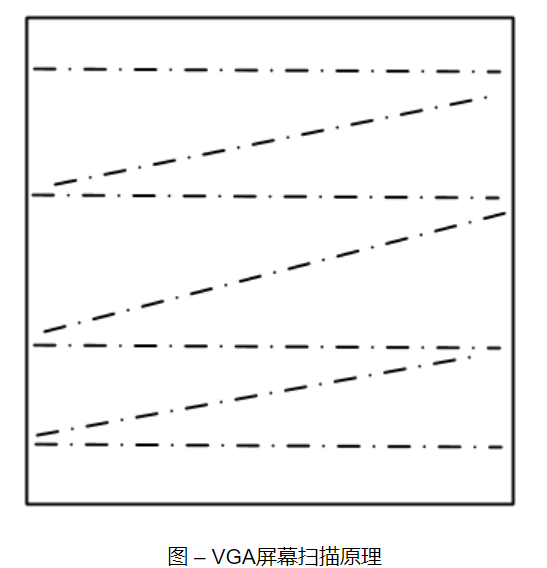

VGA在网上介绍已经烂大街了,但还是决定炒冷饭。VGA扫描显示其实就是两条线,一个是行扫描,一个是场扫描,在行有效和场有效的时候把数据发送给VGA即可显示了。显示标准就是行分辨率x列分辨率@60hz即一秒屏幕刷新60次,拿640x480@60HZ做例子,即行为640个像素,场为480个像素。

显示器扫描方式分为逐行扫描和隔行扫描:逐行扫描是扫描从屏幕左上角一点开始,从左像右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信号进行同步;当扫描完所有的行,形成一帧,用场同步信号进行场同步,并使扫描回到屏幕左上方,同时进行场消隐,开始下一帧。隔行扫描是指电子束扫描时每隔一行扫一线,完成一屏后在返回来扫描剩下的线,隔行扫描的显示器闪烁的厉害,会让使用者的眼睛疲劳。

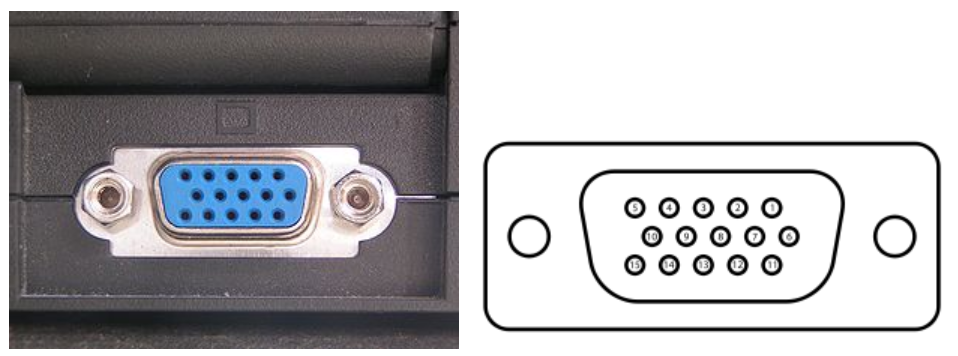

关于VGA硬件:

最主要的几根线:

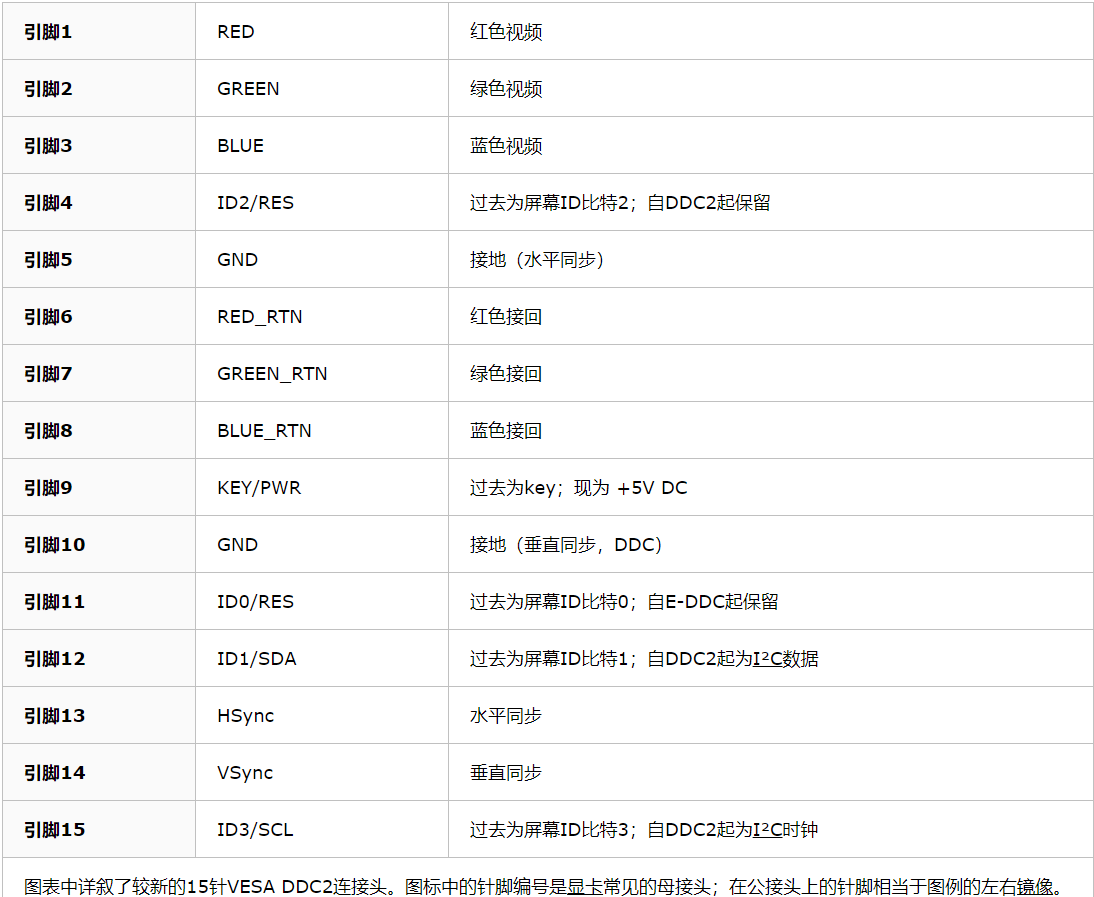

关于VGA时序分析:

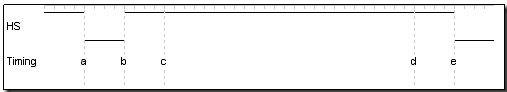

HS时序深入分析

可见时序的循环,可被划分为a,b,c,d4个时期。这四个时期定义如下:

A~B:行消隐期 即同步,相当于还原扫描坐标吧

B~C:行消隐后肩 相当于准备开始扫描吧

C~D:行显示期 扫描中,数据有效区域

D~E:行消隐前肩 完成扫描,相当于准备同步

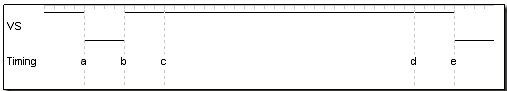

S时序深入分析

可见时序的循环,可被划分为a,b,c,d4个时期。这四个时期定义如下:

A~B:场消隐期 即同步,相当于还原扫描坐标吧

B~C:场消隐后肩 相当于准备开始扫描吧

C~D:场显示期 扫描中,数据有效区域

D~E:场消隐前肩 完成扫描,相当于准备同步

综上描述,我们只要知道每个时期的时间,便可以表示出VGA的时序。而FPGA的工作是由固定频率的时钟触发的,因此某固定时间可以用n次触发来表示。因此我们很容易就想到了FPGA常用的计数方法:比如说行扫描,我们计数0~H_total-1。用另一个进程将其划分为4个时期,按标注分配。其实这相当于状态机。

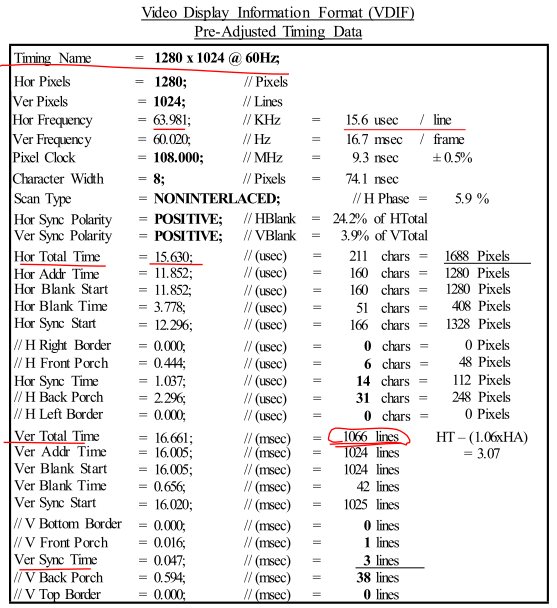

以下是固定分辨率1280*1024 60fps下HS,VS的标准:

有图可得:

①各个时期像素数:

// Horizontal Parameter( Pixel )

H_DISP = 11'd1280,

H_FRONT = 11'd48,

H_SYNC = 11'd112,

H_BACK = 11'd248,

H_TOTAL = 11'd1688,

// Virtical Parameter( Line )

V_DISP = 11'd1024,

V_FRONT = 11'd1,

V_SYNC = 11'd3,

V_BACK = 11'd38,

V_TOTAL = 11'd1066;

②像素时钟频率(即所需的VGA时钟频率)

(H_DISP + H_BACK + H_SYNC + H_FRONT)×(V_DISP + V_BACK + V_SYNC + V_FRONT)× REFRESH_RATE

在此为(1280 + 248 + 112 + 48)×(1024 + 38 + 3 + 1)× 60 = 1688 × 1066 × 60 = 107.964480 MHz (工业标准为 108.000 MHz ,当然都是能正常显示的,推荐用工业标准。)

③一帧图像的数据量(以RGB565 格式为例)

H_DISP × V_DISP × (5 + 6 + 5)bit = [H_DISP × V_DISP × (5 + 6 + 5)bit ] ÷ 8 B = [H_DISP × V_DISP × (5 + 6 + 5)bit ] ÷ 8 ÷ 1024 K

在此为 1280 × 1024 × 16 bit = 20971520 ÷ 8 B = 2621440 ÷ 1024 K = 2560 ÷ 1024 M = 2.5 M

文章来源: 博客园

- 还没有人评论,欢迎说说您的想法!

客服

客服